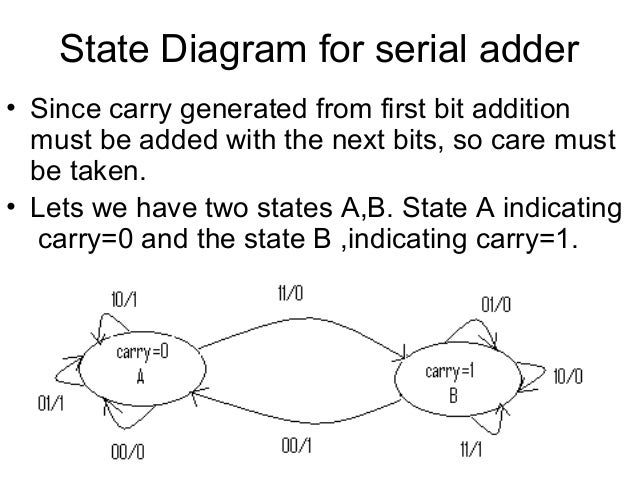

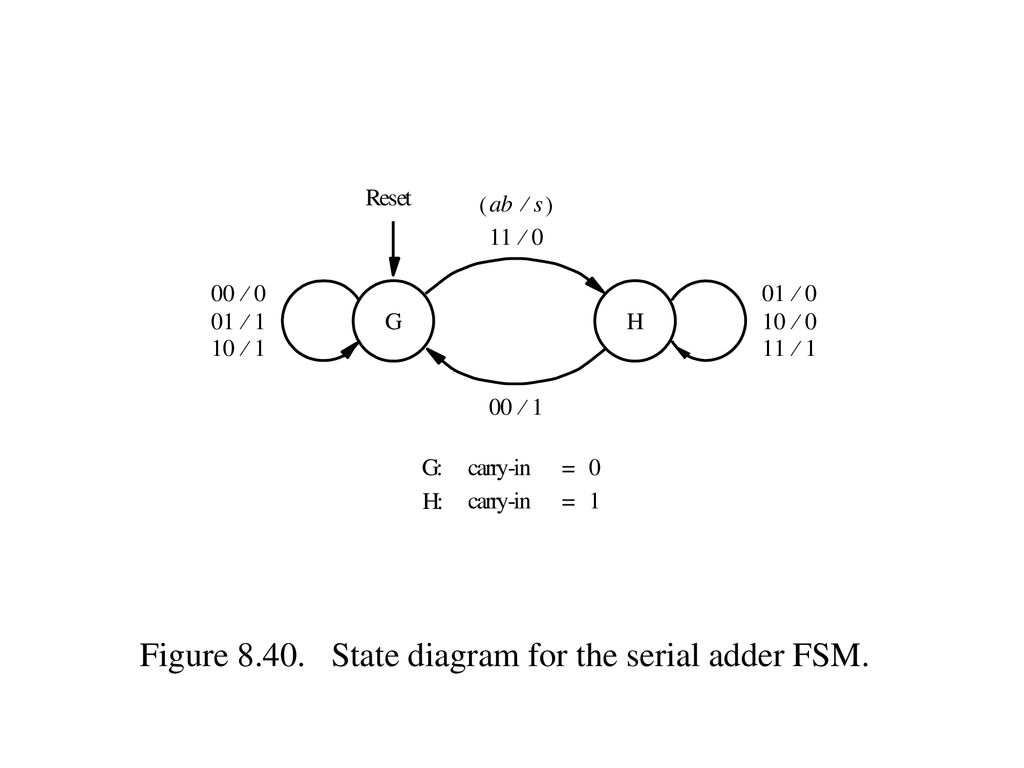

Feb 29, 2012 VHDL Code Examples for Flip Flop, Serial to Parallel Converter, 4 bit Counter, State Machine, and ADDER VHDL Code Examples VHSIC Very High Speed Integrated Circuits Hardware Description Language IEEE-1076. Yet another approach to write the VHDL code for the state machine is to create a structural model. The structural model describes all actual gates and flip-flops and their connectivity. An example of this is shown in Fig. 2-58, page 108, in the textbook. Finally, there is yet another way of describing a state machine: state machine editor. Jul 05, 2017 Moore State Machine. The Output of the State machine depends only on present state. The output of state machine are only updated at the clock edge. Let’s construct the sequence detector for the sequence 101 using both mealy state machine and moore state machine. Moore state require to four states st0,st1,st2,st3 to detect the 101 sequence. Full Subtractor Design using Logical Gates Verilog CODE. Mealy And Moore Machine Vhdl Code For Serial Adder Storify. VHDL for FPGA Design Example Application Serial Adder. The programmed geek Verilog code for serial Adder. Free Download Here pdfsdocuments2 com. Finite State Machine Serial Adder International Journal.

This page consists of design examples for state machines in VHDL. A state machine is a sequential circuit that advances through a number of states. The examples provide the HDL codes to implement the following types of state machines:

- 4-State Mealy State Machine

The outputs of a Mealy state machine depend on both the inputs and the current state. When the inputs change, the outputs are updated without waiting for a clock edge.

Vhdl Code For Serial Adder Using Finite State Machine Designer

- 4-State Moore State Machine

The outputs of a Moore state machine depend only on the present state. The outputs are written only when the state changes (on the clock edge).

- Safe State Machine

This example uses the syn_encoding synthesis attribute value safe to specify that the software should insert extra logic to detect an illegal state and force the state machine's transition to the reset state.

- User-Encoded State Machine

This example uses the syn_encoding synthesis attribute to apply specific binary encodings to the elements of an enumerated type.

Download the files used in this example:

Vhdl Code For Serial Adder Using Finite State Machine Learning

Each zip download includes the VHDL file for the state machine and its top level block diagram.

Related Links

Design Examples Disclaimer

These design examples may only be used within Intel devices and remain the property of Intel Corporation. They are being provided on an “as-is” basis and as an accommodation; therefore, all warranties, representations, or guarantees of any kind (whether express, implied, or statutory) including, without limitation, warranties of merchantability, non-infringement, or fitness for a particular purpose, are specifically disclaimed. Intel expressly does not recommend, suggest, or require that these examples be used in combination with any other product not provided by Intel.

Comments are closed.